Imperial College London

Department of Electrical and Electronic Engineering

$\rm E301$  - AO13 Instrumentation Spring 2019

Coursework Design Brief

# Contents

| 1 | ΑV                 | Vector Impedance Meter 1                    |   |  |  |  |

|---|--------------------|---------------------------------------------|---|--|--|--|

|   | 1.1                | Description                                 | 1 |  |  |  |

|   |                    | 1.1.1 Impedance vs Admittance               | 2 |  |  |  |

|   |                    | 1.1.2 Steady state Measurements             | 2 |  |  |  |

|   | 1.2                | Assignment                                  | 3 |  |  |  |

|   |                    | 1.2.1 Logistics                             | 4 |  |  |  |

|   |                    | 1.2.1.1 Groups                              | 4 |  |  |  |

|   |                    | 1.2.1.2 Laboratory Facilities               | 4 |  |  |  |

|   |                    | 1.2.1.3 Teaching Assistants                 | 4 |  |  |  |

|   |                    | 1.2.1.4 Simulations                         | 5 |  |  |  |

|   |                    | 1.2.1.5 Prototyping                         | 5 |  |  |  |

|   |                    | 1.2.1.6 Components                          | 5 |  |  |  |

|   |                    | 1.2.1.7 Assessment                          | 6 |  |  |  |

|   | 1.3                | Coursework Assignment 1 (25% of Term Marks) | 6 |  |  |  |

|   | 1.4                | Coursework Assignment 2 (25% of Term Marks) | 7 |  |  |  |

|   | 1.5                | Demo-Interview (25% of Term Marks)          | 7 |  |  |  |

|   | 1.6                | Final Report (25% of Term Marks)            | 8 |  |  |  |

| _ | DC                 |                                             | _ |  |  |  |

| 2 |                    | CB Implementation 9                         |   |  |  |  |

|   | 2.1                |                                             | 9 |  |  |  |

|   |                    | 2.1.1 Aim                                   |   |  |  |  |

|   | 0.0                | 2.1.2 Guides                                |   |  |  |  |

|   | 2.2                | Project Background                          |   |  |  |  |

|   |                    | 2.2.1 Prototyping Process                   |   |  |  |  |

|   |                    | 2.2.2 Circuit to be Implemented             |   |  |  |  |

|   |                    | 2.2.2.1 Conditions                          |   |  |  |  |

|   |                    | 2.2.2.2 Demonstration                       | 1 |  |  |  |

| 3 | Schematic Layout 1 |                                             |   |  |  |  |

|   | 3.1                | Learning Objectives                         |   |  |  |  |

|   | 3.2                | Setting Up Altium CircuitMaker              |   |  |  |  |

|   |                    | 3.2.1 Registration                          |   |  |  |  |

|   |                    | 3.2.2 Starting a New Project                |   |  |  |  |

|   | 3.3                | Schematic Layout                            |   |  |  |  |

|   |                    | 3.3.1 Add New Schematic                     |   |  |  |  |

|   |                    | 3.3.2 Adding Components                     |   |  |  |  |

|   |                    | 3.3.3 Wiring and Arrangement                |   |  |  |  |

Contents

|     | 3.3.4                    | Editing Properties                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|     | 3.3.5                    | Net Labels                                                                                                                                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|     | 3.3.6                    | Electrical Rules Check                                                                                                                                    | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| PC  | B Layo                   | $\mathbf{out}$                                                                                                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 4.1 | Learni                   | ng Objectives                                                                                                                                             | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 4.2 |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     | 4.2.1                    |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     | 4.2.2                    |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     | 4.2.3                    |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.3 | Bringi                   |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.4 |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     | 4.4.2                    |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          |                                                                                                                                                           | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 4.5 | Polvgo                   |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.6 |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 4.7 |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 2.0 |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          |                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|     |                          | •                                                                                                                                                         | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|     | 4.1<br>4.2<br>4.3<br>4.4 | 3.3.5 3.3.6  PCB Layo 4.1 Learni 4.2 Setting 4.2.1 4.2.2 4.2.3 4.3 Bringi 4.4 Routin 4.4.1 4.4.2  4.5 Polygo 4.6 Silkser 4.7 Design 4.8 Manuf 4.8.1 4.8.2 | 3.3.5 Net Labels 3.3.6 Electrical Rules Check  PCB Layout  4.1 Learning Objectives 4.2 Setting up the PCB layout 4.2.1 Units and Board Origin 4.2.2 Reshaping Board 4.2.3 Layer Stack Manager 4.3 Bringing Components In 4.4 Routing 4.4.1 Autorouting 4.4.2 Manual routing 4.4.2 Manual routing 4.4.2 Manual routing 5 Editing PCB Component Properties using Filter and Editor  4.5 Polygon Pours 4.6 Silkscreening 4.7 Design Rule Check 4.8 Manufacturing File Outputs 4.8.1 Configuring Gerber Files |  |  |

## Chapter 1

# A Vector Impedance Meter

## 1.1 Description

We are all familiar with the resistance meter, which measures the value of a resistor by applying a current and measuring a voltage. This instrument. can measure resistances but it cannot measure devices which exhibit energy storage, such as capacitors and inductors.

Many sensors, diodes and other microelectronic devices show capacitive energy storage so that they behave like one of the following:

- A capacitor with a relatively small resistor in series

- A capacitor with a relatively big resistor in parallel

Other sensing devices, such as microphones and some inertial sensors behave like lossy inductors, namely inductors in series with a resistance.

Finally, many two terminal devices display a resonant behavior, namely some sort of combination of resistance, capacitance and inductance. This is typical of coils at higher frequencies and antennas.

In most of these measurements both the real and the imaginary part of the impedance change with frequency. To determine which "equivalent circuit" model is most suitable as a model for a particular device, the measurement needs to be performed at more than one frequencies.

Specialised equipment which can measure complex voltages or complex impedances do exist; they are referred to by several different names, depending on their operation principle:

- Complex impedance meters

- Lock-in amplifiers

- Vector signal analysers

## 1.1.1 Impedance vs Admittance

In this assignment we are dealing with two-terminal devices. The concepts of impedance and admittance are interchangeable. To measure the complex impedance two tactics can be followed:

- 1. Apply a voltage and measure a current in amplitude and phase (admittance)

- 2. Apply a current and measure a voltage in amplitude and phase (impedance)

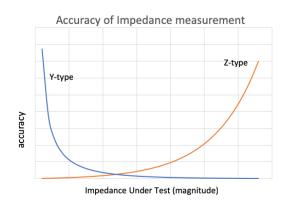

The choice of the mode of measurement is dictated by the sensitivity of the instrument used: Large in magnitude impedances are measured as impedances, while small in magnitude impedances are measured as admittances. As a rule, the accuracy of an impedance type measurement ("Z-type" apply I measure V) increases as impedance increases, and the accuracy of an admittance type measurement ("Y-type" : apply V measure I) increases as admittance increases, as illustrated below

Figure 1.1: Impedance Measurement Accuracy

## 1.1.2 Steady state Measurements

The complex impedance measurement can be performed either in the sinusoidal steady state or by Fourier transform methods. This assignment is about a steady state measurement. For a sinusoidal steady state measurement a stimulus (voltage or current) is applied and a response (current or voltage) is measured in amplitude and phase. The sinusoidal steady state measurement can be performed either as a quadrature measurement or as a polar measurement. In the quadrature measurement the phase of the stimulus is known (or measured) and the response is measured in-phase and 90 degrees out of phase relative to the stimulus. This can be done by multiplying the response with the stimulus and a 90 degree out of phase delayed copy of the stimulus, and low pass filtered.

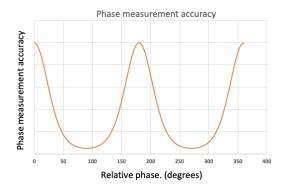

Phase measurements are also subject to some accuracy constraints. The accuracy of a relative phase measurement is maximum at 0 and 180 degrees, and degrades near 90 and 270 degrees, as illustrated below. It is often better to measure the phase difference to 90 degrees out of phase of the reference!

FIGURE 1.2: Phase Measurement Accuracy

In a polar measurement the amplitude of the response is measured, e.g. with an RMS detector, and then the phase with a phase detector or a phase-locked-loop.

## 1.2 Assignment

Design simulate, prototype and demonstrate a complex impedance measurement instrument which can:

Measure Impedance:

- Spot frequencies of 1kHz, 10kHz, 100kHz, (+optionally 1MHz)

- Impedance magnitudes from 10 Ohm to 1 M Ohm

- Impedance or admittance phase from -180 degrees to 180 degrees with 5 degrees accuracy.

These specifications cannot be achieved with a single range, either in magnitude or phase measurement.

The instrument should, therefore, be capable of switching between different modes of operation automatically under microcontroller control.

Controls for frequency, amplitudes, gains, etc. to allow range changes as necessary to achieve the stated range and specifications must be provided.

An NXP MBED LPC1768 is recommended and supplied but any other microcontroller may be used. Dedicated GTA support is available to help you with the microcontroller subsystem.

Please note that marks will be awarded for effort and above all good and innovative design decisions justified by analysis and sound reasoning. A non-operational instrument, but one which is well engineered and well explained, may earn higher marks than an operational but poorly designed and inadequately explained and documented one.

### 1.2.1 Logistics

#### 1.2.1.1 Groups

The work will be carried out in groups of 2 students. The group membership will be declared by email to me (c.papavas@imperial.ac.uk) by **Monday January 21st**. Students not members of a group by 21/1 should email me asking to be grouped.

### 1.2.1.2 Laboratory Facilities

All work will be in the 2nd year lab area on level 1. We have priority over the last three benches on the side closest to the windows. Power supplies, oscilloscopes, signal generators and digital multimeters are available, as well as RLC meters for reference and calibration. **Please avoid** using the Level 5 lab, which is reserved for final year projects.

#### 1.2.1.3 Teaching Assistants

The GTAs for this course, and their primary areas of expertise, are as follows.

Yacub Szypicyn jakub.szypicyn13@imperial.ac.uk Lab Work Akshayaa Pandiyan a.pandiyan@imperial.ac.uk Lab Work

Daryl Ma jianwen.ma13@imperial.ac.uk Printed Circuit Boards

Amir Nassibi a.nassibi15@imperial.ac.uk Microcontrollers

Surgeries in the lab with the GTAs will be announced.

#### 1.2.1.4 Simulations

The Linear Technology LTSpice, is a free, favourite among professionals, simulator. LTSpice has a Wiki and a web users group with extensive resources, including tutorials. PSPICE is a licensed simulator available in the laboratory computers.

### 1.2.1.5 Prototyping

Circuit development will carried out on breadboards. However, the row-to-row capacitance of these is high enough to severely limit the performance of an instrument made on breadboard. For this reason you will make your final device on a printed circuit board (PCB). PCBs will be 2 layer, plated through hole, and will be manufactured at Newbury Electronics PCB train Express (http://www.pcbtrain.co.uk). PCBs will be designed using any PCB design software you wish. The license-free Altium Circuit Maker software will be taught and supported by a GTA. Each group will do their own assembly. Whenever possible please use through-hole components to make assembly easier. There will be two PCB design submissions, associated with the two report submission deadlines:

- February 4th: Tutorial board and draft electronics design

- March 4th: Final instrument design.

Boards will be available to groups for assembly one after submission. Submissions will be checked for errors, and may be returned to the groups for corrections before they are sent for fabrication.

## 1.2.1.6 Components

Each group will have a budget of £40 for components. Additionally to this budget each group will be allocated an NXP LPC1768 microcontroller and a breadboard. Components (preferably from RS and Farnell for rapid delivery) will be ordered by groups

directly through the Department Stores, and charged to "UG teaching 3rd year, E302"

A spreadsheet with orders will be submitted with the final report. Budget overruns without prior approval will incur a marks penalty.

#### 1.2.1.7 Assessment

There will be three reports and one interview. The following is a list of course deadlines:

- 1. First Report PCB with microcontroller (25%). Due Monday 4/2 before class.

- 2. Second Report (25%). Due Monday 4/2 before class.

- 3. Demo / Interview (25%) during last week of Term 21-22/3 (To be arranged)

- 4. Final Report (25%). Due by 5pm on 22/3

## 1.3 Coursework Assignment 1 (25% of Term Marks)

A brief report of up to four pages (including figures), handwritten-scanned or typeset with 10pt minimum font, is due on Blackboard by Monday February 4th by 9AM.

#### Contents:

- Design overview

- Operating Principle

- modes of operation

- accuracy estimates

- System block diagram

- Analogue Interface circuit schematic design

- PCB files for microcontroller first draft of analogue interface

This report should be up to four pages plus a zip file containing the PCB manufacturing files (Gerbers) plus PDFs of the schematic and the metal layers.

• Scanned handwritten submission will be accepted

- The 4 page limit includes all figures and tables.

- No appendices will be accepted. Any appendices submitted will be ignored.

## 1.4 Coursework Assignment 2 (25% of Term Marks)

A brief report of up to six pages (including figures), handwritten-scanned or typeset with 10pt minimum font, is due on Blackboard by Monday March 4th by 9AM.

#### Contents:

- Photograph of assembled first PCB

- Measurements of first PCB

- Final Schematic diagrams

- Final PCB design, pictures of top and bottom metals.

- High level description of microcontroller code

This report should be up to six pages plus a zip file containing the PCB manufacturing files (Gerbers) plus PDFs of the schematic and the metal layers.

- Scanned handwritten submissions will be accepted

- The six page limit includes all figures and tables.

- No appendices will be accepted. Any appendices submitted will be ignored.

## 1.5 Demo-Interview (25% of Term Marks)

A group interview the Course Leader and a GTA will be scheduled at a convenient time during the last week of term, between Thursday March 21th and Friday March 22nd. The interviews will be scheduled by electronic signup on a first come, first serve basis.

The interview will last half an hour.

During the interview you will be asked to demonstrate the operation of your instrument on 2-3 unknown devices supplied by the examiners.

### Agenda:

- Describe your instrument

- Demonstrate operation with your own DUT

- Measure two unknown DUTs

Marks will be awarded for:

- Smooth operation of the instrument

- Accuracy of determining the DUT impedance.

## 1.6 Final Report (25% of Term Marks)

A final report detailing the design, any simulations, and measurements is due by 5pm on Friday March 22nd.

The report must be at most ten pages long including figures and diagrams, It may be handwritten- scanned or typeset with 10pt minimum font.

The report must contain:

- Final schematic diagrams if changed since 2nd report

- Photograph of the prototype.

- List of input and output signals of the instrument.

- Specifications achieved

- Simulations (if available)

- Bill of materials and total cost of orders submitted.

- Graphs of measurements covering the range achieved.

- Algorithm or pseudocode for calibration, self calibration, automation.

- Group Member roles contributions

This report should be up to TEN pages plus a pictures of the schematic, and the PCB.

- Scanned handwritten submissions will be accepted

- The ten page limit includes all figures and tables.

- No appendices will be accepted. Any appendices submitted will be ignored.

# Chapter 2

# **PCB** Implementation

## 2.1 Information

### 2.1.1 Aim

Learn the full process of designing a printed circuit board with Altium Circuitmaker.

#### **2.1.2** Guides

There are a few helpful guides that will be useful:

- 1. CircuitMaker Documentation<sup>1</sup>

- 2. CitcuitMaker FAQs<sup>2</sup>

- 3. The Circuit Designer's Companion by Tim Williams

Additionally, you can approach your GTAs with any questions. For computer related issues, you can contact the Computer Support Group.

<sup>&</sup>lt;sup>1</sup>https://documentation.circuitmaker.com/display/CMAK/From+Idea+to+Manufacture+-

<sup>+</sup> Driving + a + PCB + Design + through + Circuit Maker

<sup>&</sup>lt;sup>2</sup>https://documentation.circuitmaker.com/display/CMAK/CircuitMaker+-+((FAQs))

## 2.2 Project Background

## 2.2.1 Prototyping Process

In this exercise, the aim is to design a prototype that will fulfill its specifications, likely under fixed laboratory conditions. There can also be circuit design for production-ready circuits, but we will not cover that here.

The process for integrated circuit design generally follows this format:

- 1. Gathering Specifications/Requirements for Device

- 2. Determine components capable of meeting these requirements

- 3. Simulation of theoretical circuit

- 4. Printed Circuit Board Implementation

- 5. Testing and Validation

- 6. Reiteration for new improved Device

These set of notes would cover only the Printed Circuit Board implementation area, and mainly involve schematic entry, PCB layout, and the relevant design rules checks.

## 2.2.2 Circuit to be Implemented

#### 2.2.2.1 Conditions

There will be some fixed conditions:

- 1. Control unit would be the LPC1768 Development Board.<sup>3</sup>

- 2. Only Through-Hole components.

- 3. Two-sided board with vias.

- 4. Board Size of 100mm x 100mm

- 5. Use components from Linear Technology and Analog Devices

These conditions should be followed to the best of your ability. In the event that you would like to use other choices, approach the GTAs to let us know. The remaining circuit would be left to your creativity.

$<sup>^3</sup>$ https://www.nxp.com/products/processors-and-microcontrollers/arm-based-processors-and-mcus/lpc-cortex-m-mcus/lpc1700-cortex-m3/arm-mbed-lpc1768-board:OM11043

## 2.2.2.2 Demonstration

To demonstrate an example, the circuit to be implemented would consist of the LPC1768 Development Board, with a 40-pin dual in-line package socket to plug the board. Following on, two external LEDs would be used to provide visual indicators, and a potentiometer would be used to provide a variable voltage input to be read on one of the pins.

# Chapter 3

# Schematic Layout

## 3.1 Learning Objectives

- How to set up CircuitMaker

- How to add new schematics and components

## 3.2 Setting Up Altium CircuitMaker

## 3.2.1 Registration

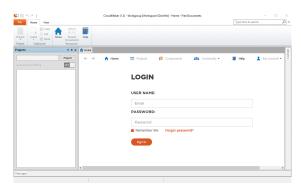

First, you'll have to set up your account. Sign up for an account through this link <sup>1</sup>. Once that is done, go ahead and login. Start the CircuitMaker app on windows, and the login page should show up as shown in Fig. 3.1. Sign In.

FIGURE 3.1: Login Screen

<sup>&</sup>lt;sup>1</sup>https://workspace.circuitmaker.com/Account/SignUp

## 3.2.2 Starting a New Project

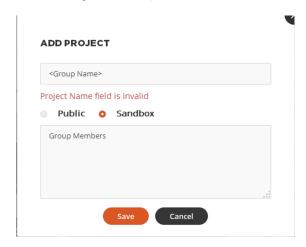

To create a new project, click on  $Add\ New\ Project$  in the home screen, or  $\underline{\text{File}} \to \text{New\ Project}$ . In the window that appears as shown in Fig. 3.2, type your group name in the name field, and the members names in the description. Set the privacy settings to sandbox.<sup>2</sup> Click Ok. On the next Edit Project screen, click Save.

FIGURE 3.2: New Project Screen

## 3.3 Schematic Layout

### 3.3.1 Add New Schematic

You will see a Projects Panel appear as shown in Fig. 3.3. To add a schematic to your project, click on  $\underline{\text{Home}} \to \text{Projects} \to \text{Add new Schematic}$ . As this schematic will contain the control unit, enter the schematic sheet name as  $Control\_Unit$ , and click ok.

## 3.3.2 Adding Components

CircuitMaker has an advantage of being closely tied to an online component search engine database(Octopart). That means commonly used components would likely have their schematics and PCB footprints already created and stored on the cloud. However, always check that the schematic matches the datasheet of the chosen component. There are multiple revisions of a single component, and you will never know if a pin is switched on a new revision. Checking and making sure that the schematic is correct now would minimise mistakes later.

<sup>&</sup>lt;sup>2</sup>This makes the design private, and only allows people given permission rights to view or edit the project.

FIGURE 3.3: Projects Panel

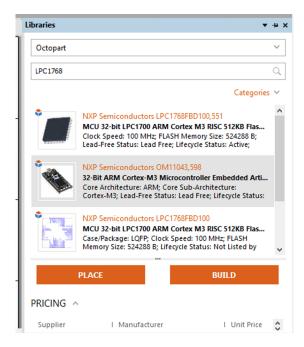

To open the library panel, click on  $\underline{\text{View}} \to \underline{\text{Libraries}}$  as shown in Fig. 3.4. Change the library to Octopart, and type in LPC1768. Select  $\underline{\text{NXP}}$  Semiconductors OM11043, 598, and click Place. As you move your mouse cursor over the blank schematic, you should observe the schematic model of the LPC1768 Evaluation Board. Click to Place.

FIGURE 3.4: Adding Components

Repeat the following for the additional components:

• 2 x 220R through-hole resistors

- 2 x LED

- 1 x potentiometer

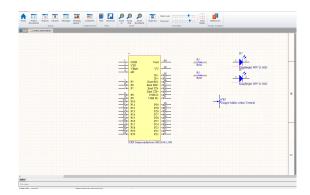

You are free to choose any components you like, as long as they abide by the conditions given beforehand. You should have something like this as shown in Fig. 3.5.

Figure 3.5: Components on Schematic

## 3.3.3 Wiring and Arrangement

It is good practice to have a clean schematic - Having multiple wires criss-crossing, or components that should be near each other placed far away should be avoided as much as possible. As circuits increase in complexity, having a clean schematic would improve the speed of analysis and help aid good design.

Let's begin by arranging the components where they should be. First, the 2 LEDs and their resistors would be placed near P5 and P6. These are chosen as P5 corresponds to I/O 0 of the microcontroller, and P6 corresponds to I/O 3.

Next, place the potentiometer next to P16. This is chosen as P16 corresponds to the Analog to Digital Converter (AD0.1) on the microcontroller.

Finally, add in ground and power ports. To add the ground port, Right Click  $\rightarrow$  Place  $\rightarrow$  Place GND power port or use the shortcut  $\underline{Z}$ . For a power port, Right Click  $\rightarrow$  Place  $\rightarrow$  Place VCC power port or use the shortcut  $\underline{V}$ .

As the development board would have two means of being powered, either through the USB connector located on the board, or through the VIN pin located on the board, we should clearly demarcate the different power supplies. Additionally, the development board supplies its own 3V3 supply.

Connect a power port named  $3V3\_OUT$  to the *Vout* pin. Likewise, do the same for the VIN pin with a power port named  $5V\_EXT$ .

Once the components have been arranged neatly, begin wiring the circuit up using the shortcut W. Once done, place a directive for no Electrical Rules Check(ERC) on pins of the development board that will not be used. This will allow any errors that may flag up from the ERC due to there not being any pins connected being removed. To do so, go to Right Click  $\rightarrow$  Place  $\rightarrow$  Directives  $\rightarrow$  Generic No ERC.

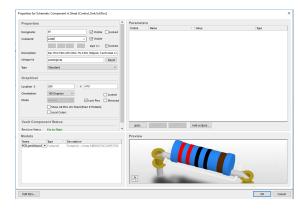

## 3.3.4 Editing Properties

Lastly, to edit the components individually, Right Click on the component and go to Properties. A window as shown in Fig. 3.6 should appear. In this window, edit the comment field to reflect the values of the passive components you are using. A useful trick to check the component is also in the preview window, where you can view the 3D model of the component you are using. Hold shift and right click on the figure in the preview window to view the component from different angles. You can also click on the hammer logo on the bottom left to change the view to a 2D view. This allows you to take a look at the footprint of the component as shown in Fig. 3.7.

FIGURE 3.6: Properties Window

FIGURE 3.7: 2D Image

#### 3.3.5 Net Labels

Net labels are helpful to determine where each wire leads to. This has an added advantage later in the PCB layout, and having a name for each wire allows you to differentiate

them correctly. To add net labels, use the shortcut  $\underline{N}$  and add it to the wires you would like to label.

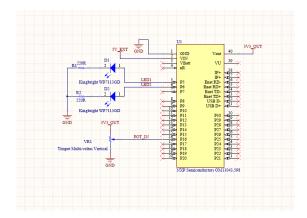

Once that is done, finish off by annotating the components. This can be done by  $\underline{\text{Tools}} \to \text{Annotate} \to \text{Annotate Schematics Quietly}$ . The finalised schematic can be seen in Fig. 3.8.

FIGURE 3.8: Completed Schematic

#### 3.3.6 Electrical Rules Check

To begin the electrical rules check, you would have to save and commit the project first. Do this by going to  $\underline{\text{Project}} \to \underline{\text{Save Project}}$ , and then  $\underline{\text{Project}} \to \underline{\text{Commit Project}}$ . Additionally, go to  $\underline{\text{View}} \to \underline{\text{Messages}}$  to observe any error messages that may pop up during compilation. Finally, use the shortcut  $\underline{F9}$  to compile the project.

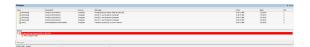

An example of an error is displayed here in 3.9. If errors occur, check and see if they are critical or non-critical errors.

FIGURE 3.9: Error Message

Once your project has compiled successfully, you are ready to begin with the PCB layout.

## Chapter 4

# **PCB** Layout

## 4.1 Learning Objectives

- How to set up the PCB Layout before design

- How to transfer the schematic to layout

- How to route manually and automatically

- How to utilise polygon pours

- How to apply silkscreening

- How to perform the Design Rules Check

- How to obtain the manufacturing file Outputs

## 4.2 Setting up the PCB layout

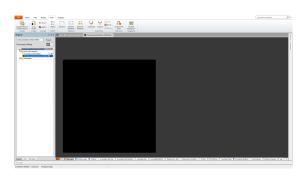

First, we'll have to add a new .CMPcbDoc to the project. Go to  $\underline{\text{Home}} \to \text{Add New PCB}$  and enter the new file name as the same name as your group name. Once done, you should observe a black board layout with a white dotted line demarcating the edges.

## 4.2.1 Units and Board Origin

Before we begin, we will change the grid size from imperial units to metric. This helps obtain a better feel for the board size, as we are now dealing with the physical representation of the PCB. Go to  $\underline{\text{Home}} \to \underline{\text{Board}} \to \underline{\text{Board Options}}$  and change the measurement units from Imperial to Metric as shown in Fig.4.2.

FIGURE 4.1: New PCB Document

FIGURE 4.2: Changing Setting to Metric

Next, set the origin to the bottom left point of the board cutout. Go to  $\underline{\text{Home}} \to \underline{\text{Grids}}$  and units  $\underline{\to}$  Origin & Jumps  $\to$  Set and click on the point where you want your origin to be. The bottom left corner is chosen here and all component locations would now be referred to from this point.

## 4.2.2 Reshaping Board

The default board shape is larger than what is required. Since the size of the components are already known, we will reshape the board shape to a smaller size to minimise space. Let's redefine the board size to  $50 \times 80 \text{mm}$ . First, let's change the snap grid size to 2.5 mm to make it easier to mark out the edges. Go to  $\underline{\text{Home}} \to \text{Grids}$  and  $\underline{\text{Units}} \to \text{Snap Grid}$ , and change the field to 2.5 mm.

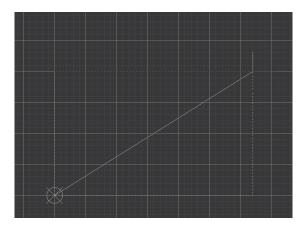

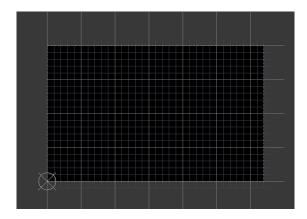

Next, go to  $\underline{\text{Home}} \to \text{Board Shape} \to \text{Redefine Board Shape}$ . This begins off from the origin, and you can set the board shape by clicking on the other 3 corners that you would like as seen in Fig. 4.3. Use the X and Y coordinates at the bottom left of the window to help you define the distances correctly. Fig. 4.4 displays the new board shape.

## 4.2.3 Layer Stack Manager

Go to  $\underline{\text{Home}} \to \text{Board} \to \text{Layer Stack Manager}$  to observe the physical layers of the PCB as shown in Fig. 4.5. The default settings should correspond to a two layer board, with a top and bottom signal layer between a FR-4 dielectric core. We will not go into too much detail here, but note that you can change the number of layers on the board as you see fit.

<sup>&</sup>lt;sup>1</sup>In addition to this, most PCB manufacturers charge by the size of the PCB. Having a smaller PCB essentially also equates to a less expensive one.

FIGURE 4.3: Changing Board Shape

FIGURE 4.4: Board Shape Complete

FIGURE 4.5: Layer Stack Manager

Next, we will have to set up the design rules for the project. Design rules here are the rules that determine the minimum clearance between tracks, how small the via diameter can go, or the minimum angle between tracks allowed. These are generally determined by the manufacturer, whose tooling machines have a physical limit to their performance. Before starting any design, always go through the PCB manufacturer's design specifications before routing the components.

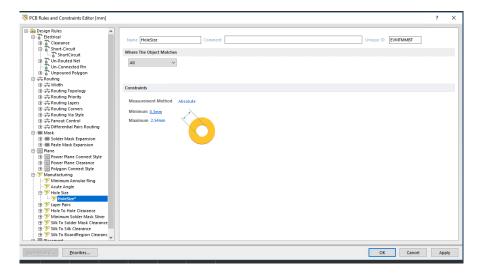

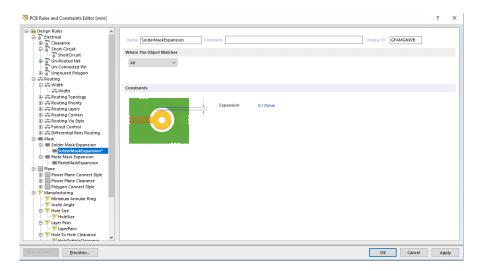

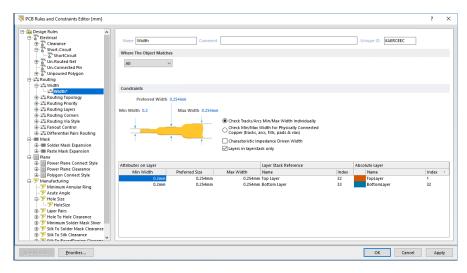

For this project, we will be going with PCB train specifications<sup>2</sup>. Change the following parameters:

- 1. Manufacturing Hole Size

- 2. Solder Mask Expansion

- 3. Minimum Routing Width

Fig. 4.6, 4.7 and 4.8 give an impression of the values chosen for this project. However, check through the specifications and understand the rationale behind these chosen values.

FIGURE 4.6: Via width change

FIGURE 4.7: Solder Mask change

Once this is done, we can finally move on to bringing the components into the layout editor.

<sup>&</sup>lt;sup>2</sup>https://www.pcbtrain.co.uk/resources/pcb-technical-capability

FIGURE 4.8: Minimum Track Width

## 4.3 Bringing Components In

To import the schematic capture components to the PCB document, first click on the Control\_Unit.SchDoc in the Projects Panel. From there, go to  $\underline{\text{Home}} \to \text{Project} \to \underline{\text{Update PCB Document in ¡Group Name¿.PrjPcb.}}$  An Engineering Change Order(ECO) window should appear as shown in Fig. 4.9. Click on validate changes, then execute changes. Validate changes flags any modifications done to the schematic, and allows you to observe any changes in the wiring if it has been done. Executing the change performs this change in the PCB layout itself.

FIGURE 4.9: Engineering Change Order

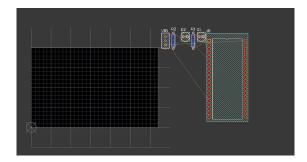

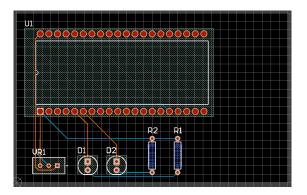

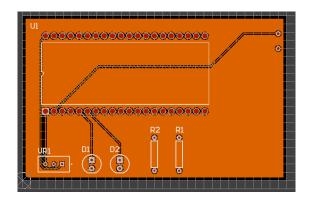

Navigate back to the PCB layout editor, where you should now observe the components as shown in Fig.??. You can then use the shortcut <u>3</u> or <u>2</u> to toggle between 2D view modes and 3D view modes respectively. Note that the 3D view mode effectively acts as a viewer, but to ensure grid locations are met, components should mainly be edited in the 2D view mode.

Similarly, begin by arranging the components to their ideal locations. An example would be for external wire connections to be connected to the edge of the board. In this case, the USB cable supplying the power should be as close to the edge of the board

FIGURE 4.10: Components added to PCB layout

as possible. Change the snap grid to 0.5mm, and use shortcuts such as <u>spacebar</u> while editing the components to rotate them.

There are small lines linking the pins together. These lines are termed "Rats Nest". These lines should be kept as short as possible to minimise routing lengths.

## 4.4 Routing

There are two methods of routing - Automatic or manual. Automatic leaves the control of the routing paths to the software itself, and churns out routes. This gives the designer the ability to save design time at a cost - these paths may sometimes not be the most efficient route to the pin, or the software does not have an idea of the best board layout management practices. Sometimes, autorouting leaves the designer with more work to do simply correcting the non-optimised routes. Hence, manual routing also gives a choice of absolute control to the designer for the most efficient and optimised layout as per the designer's wishes.

#### 4.4.1 Autorouting

For a simple board in this demonstration, autorouting would serve the purpose as there are few enough routes for the designer to check.

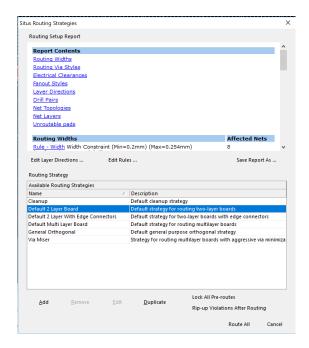

For autorouting, go to  $\underline{\text{Tools}} \to \text{Autoroute} \to \text{All}$ . In the pop up window that appears, leave the default 2 layer board strategy as shown in Fig. 4.11. Then click on Route All to let the autorouter do so. Fig.4.12 displays the board layout after autorouting has completed.

FIGURE 4.11: Autorouting Setup

FIGURE 4.12: After Autorouting

#### 4.4.2 Manual routing

Now, to demonstrate manual routing, two additional vias for the 5V external supply will be added. These allows for use cases when the USB input is not available.

## 4.4.2.1 Editing PCB Component Properties using Filter and Editor

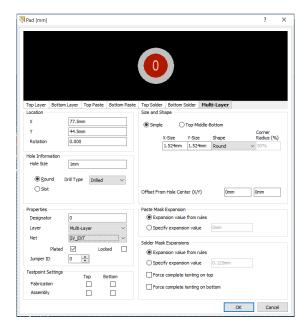

Go to  $\underline{\text{Home}} \to \underline{\text{Pad}}$  and click to add two pads, preferably at the edge of the board. Next, we will edit the properties of these two pads to a size that will be easy to connect external wires from a power supply to.

One useful tool to use is the filter tool. This allows the designer to filter out components in the design that should be edited, and allows you to edit these components at the same time.

Go to  $\underline{\text{View}} \to \underline{\text{Filter}}$ , and select  $\underline{\text{Free}}$  for Groups and  $\underline{\text{Pad}}$  for Objects as illustrated in Fig. 4.13. This will highlight the two pads you have just added, as they have not been connected to any other nets yet. Select these two pads.

FIGURE 4.13: PCB Filter Tool

Now, navigate to the PCB panel on the bottom left of the screen as shown in Fig. 4.14. Change the field to Hole Size Editor at the top, and change the Condition Selection to Show selected Objects. This should give you the 2 holes in the middle panel. Now, change the sizes from 0.762mm to 1mm by typing into the Hole Size field. Select yes on the Confirm hole size modification window. This will edit the two pads at the same time, and is a useful tool for editing large numbers of components at once.

FIGURE 4.14: PCB Editor Tool

Next, we will assign nets to these pads. At the moment, these pads are not connected (NC), and are given arbitrary numbers. Change the net under properties to 5V\_EXT. For the other pad, change the net to GND as shown in Fig. 4.15.

FIGURE 4.15: Changing the Net

The rats nest should pop up, indicating the closest 5V-EXT net and GND net to the pads. To manually route them, use the shortcut  $\underline{R}$  and click on the pads. Doing so would highlight the net that is selected, allowing the designer to view the best possible link available.

To change layers, use the tabs at the bottom of the screen. To route to the bottom layer, select the bottom layer tab at the bottom of the screen, and route as normal.

FIGURE 4.16: Bottom Layer Routing

This process of adding pads can also be applied for adding testpoints. With more complicated circuits, adding more testpoints for the prototype is ideal to improve the speed and ease of testing. Having a pad to apply a probe and another pad to apply the GND to is much simpler than having to solder wires to make the connections.

## 4.5 Polygon Pours

Polygons is the term given to large copper areas used to provide a common net. Usually, the ground or power net is used as the polygon pour, for signal noise reduction or heat dissipation reasons. Go to Home  $\rightarrow$  Pour  $\rightarrow$  polygon Pour.

On the Polygon Pour screen, we will add the polygon. Change the Name to <u>Top Layer - GND</u>, and the Layer to <u>Top Layer</u> as shown in Fig. 4.17. For the Connect to Net option, set it to GND. Click Ok.

FIGURE 4.17: Polygon Pour Setup

Select the four corners for the polygon pour, and then press Esc to end the process. The polygon pour should automatically fill the gaps in the board a shown in Fig. 4.18.

FIGURE 4.18: Polygon Pour Result

Note in Fig. 4.18 that there's a block of polygon that is not connected to any net. This is what is termed an island. To get rid of these, select the polygon, and right click to access its properties. Change the *Remove Islands Less than ¡field¿ (sq.mms) in Area* field to 10 as shown in . Click ok, and proceed to repour. This should remove the islands as shown in Fig. 4.20.

## 4.6 Silkscreening

The silkscreen is the visual interface of the board to the user. A good silkscreen would make the board easy to understand and use, and reduces any mistakes after the board

- Remove Islands Less Than

10 (sq. mms) In Area

- Arc Approximation

Maximum Deviation From Perfect

Arc 0.013mm

- Remove Necks When Copper

Width Less Than 0.25mm

FIGURE 4.19: Removing islands

FIGURE 4.20: Polygon Pour after Islands Removed

ends up in the hands of a designer. Be as artistic as you can, and enjoy the process.

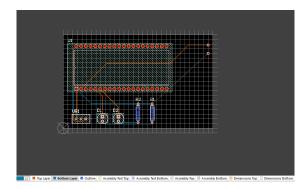

Navigate the bottom tabs to the Top Overlay. Go to  $\underline{\text{Home}} \to \underline{\text{Place}} \to \underline{\text{Text}}$  to add the text in. Now, you can add in any text you want. You can vary the size of the font in properties, or change the font type. This is up to your own discretion.

## 4.7 Design Rule Check

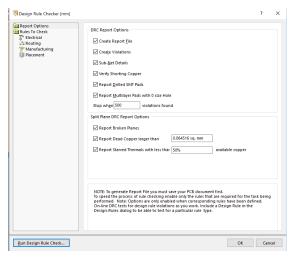

Once you are ready to proceed, run the Design rules  $\operatorname{check}(\operatorname{DRC})$  to ensure that the board layout meets the required standards. Go to  $\operatorname{Outputs} \to \operatorname{Reports} \to \operatorname{Design} \operatorname{Rule} \operatorname{Check}$ . As we have set up the rules previously, go ahead and Run Design Rule Check.

A DRC report should appear as shown in Fig. 4.22. Understand the errors, and fix them. For the warnings, try to minimise them as much as possible.

FIGURE 4.21: DRC Check

FIGURE 4.22: DRC Report

## 4.8 Manufacturing File Outputs

There are a number of outputs you can generate. **Assembly Outputs** refer to files used by a pick and place machine for auto-assembly. **Documentation Outputs** provide the schematics and PCB drawings for analysis. **Fabrication outputs** provide the files and guides for the drilling required for the pad locations. Finally, **Report Outputs** provide the rules check, as well as the Bill of Materials(BOM) regarding the components used on the board.

## 4.8.1 Configuring Gerber Files

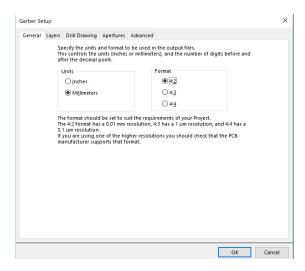

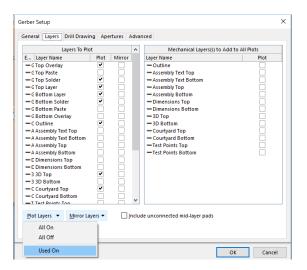

In this project, we would need to obtain the Manufacturing Outputs, which take the form of Gerber files. First, Go to  $\underline{\text{Outputs}} \to \underline{\text{Gerber}}$ . Under General, change the units to Millimeters, and the Format to 4:3.

Under the Layers tab, select Plot Layers, and click used on.

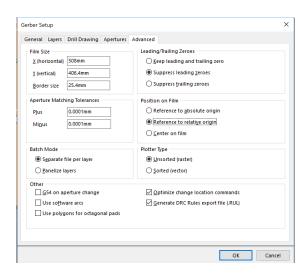

Finally, go to advanced tab, and check the *Reference to relative origin* circle. Once this is done, click OK.

FIGURE 4.23: Gerber Setup for Millimeters and Resolution

FIGURE 4.24: Gerber Setup for Layers

Figure 4.25: Gerber Setup for Relative Origin

## 4.8.2 Configuring Output Files

Go to  $\underline{\text{Project}} \to \text{Generate Outputs}$ . Commit and save your project as required. Check the Schematic Prints, Board Information, Gerber Files and NC Drill Files for the outputs, and Generate. This should produce a zip file. Download it.

FIGURE 4.26: Generate the output files

## 4.8.3 One Last Check

Use a gerber viewer to see if the files has exported correctly. You can do this by using an online tool<sup>3</sup> to see if the drill holes correspond correctly to your project.

<sup>&</sup>lt;sup>3</sup>http://www.gerber-viewer.com/